# On the Characterization and Manipulation of Interfaces in Organic and Hybrid Electronic Devices

by

### Josué F. Martínez Hardigree

A dissertation submitted to The Johns Hopkins University in conformity with the requirements for the degree of Doctor of Philosophy

Baltimore, Maryland

December 2014

© Josué F. Martínez Hardigree

All rights reserved

#### Abstract

Organic electronics comprises a field of study at the intersection of chemistry, physics, electrical engineering, and materials science focused on the development of electronic devices in which the active charge transporting materials are composed of organic conjugated molecules. This field has grown out of an interest in harnessing many attributes of organic materials not readily available to inorganic semiconductors, including: low synthesis temperatures for organic compounds; a nearly infinite combination of chemical moieties with similar conjugated character; and ease of fabricating thin films of organic compounds through both vacuum and solution processes. These properties make the fabrication of low-cost, highly-customizable electronics commercially viable, despite their inferior carrier transport to crystalline inorganic semiconductors. This key hurdle—understanding charge transport in organic molecules and thin films made from them—has become a primary research objective in the field.

Understanding charge transport in organic electronic devices spans analysis across various size scales, each contributing to the observed behavior of an electronic device:

- The chemical structure of the constituent conjugated molecules (Ås)

- The arrangement of these molecules into ordered and disordered regions within a thin film (10s of Ås)

- The configuration of the thin film within the working device (100s of Ås)

At each of these scales, the concept of an interface acquires new meaning, scaling from van der Waals forces between molecules, to grain boundaries in polycrystalline materials, and incrementally to device-scale junctions between dissimilar materials. Because each of these interfaces can promote or inhibit carrier transport within an electronic device, a complete understanding of carrier transport in organic semiconductors (OSCs) demands comprehensive characterization of interfaces at each of these scales.

The subject of this thesis is a critical examination of the insulator-OSC interface in the context of several electronic device architectures. The properties of this interface are of paramount importance in organic field-effect transistors (OFETs), where the low intrinsic carrier mobilities of OSCs renders them highly susceptible to even the most marginal deviations from an ideal interface. As a result, transistor switching characteristics quickly carry through to circuit-level reliability and power consumption. This dissertation aims to demonstrate the use of existing materials in new ways for exercising nanoscale control over this interface, with an eye towards understanding their individual and collective charge transport behavior.

Chapter 1 reviews the state of the art in control over the threshold voltage of OFETs, of which two methods—dipolar self-assembled monolayers (SAMs) and electrostatic poling—are considered in the subsequent chapters. Chapter 2 details the use of SAMs of dipolar alkylsilanes as a surface treatment for tuning  $V_T$ , reducing leakage currents, and improving switching efficiency. Increases in field-effect transconductance in SAM-treated OFETs are shown to be consistent with the presence of additional surface states.

Chapter 3 details an approach to decouple the relative contributions of the insulator/SAM and SAM/OSC interfaces from the capacitive responses of the OFET multilayer, and is compared to recent theoretical predictions of increased energetic disorder in SAM-treated OSC layers. Increased mobility of equilibrium carriers as measured with charge extraction are compared to OFET measurements and are shown to further reinforce the notion that larger molecular dipoles contribute to enhanced carrier transport through changes in the energetic disorder at the insulator/OSC interface. In Chapter 4 electrostatic poling, or gate stressing, of lateral OFETs is explored. A Poisson's equation model is applied to surface potential images of stressed lateral OFETs and shown to accurately predict the observed threshold voltage shift. Lastly, Chapter 5 presents future directions for the study of SAM-treated interfaces using charge extraction, with a focus on the use of SAMs as remedial layers for marginal quality OSCs. In addition, the potential of surface potential-derived charge densities for sensing applications is discussed.

Prof. Howard E. Katz (Advisor)

Prof. Susanna M. Thon (Reader)

#### Acknowledgements

Although a thesis is submitted to fulfill the graduation requirements of a single individual, it bears the marks of many. I would like to thank first and foremost my advisor, Howard E. Katz. Throughout my studies he created an environment that combined active scientific guidance with considerable freedom to explore the questions in organic and hybrid electronics that piqued my interest. This philosophy and approach to advising contributed immensely to my development as a scholar, and equally to my personal growth during the five and a half years of my graduate training.

I am grateful to my fellow colleagues in the Katz group for entertaining my questions and midnight brainstorming sessions. Dr. Bal Mukund Dhar served as both mentor and energetic rumination partner during my first two years, and our initial work on self-assembled monolayers laid the foundation for what was to become my dissertation. I had the great opportunity of collaborating with Dr. Tom J. Dawidczyk, and am thankful for his willingness to let me explore the immense amount of data on lateral transistors he had acquired during his doctorate. I was fortunate to carry out my first synthesis of an organic semiconductor under the guidance of Dr. Jasmine Sinha, whose talent in chemistry cannot be overstated. I had the opportunity to mentor Robert M. Ireland during his first year in our group, and since that time I have learned as much from him as I hope he has learned from me.

To Matthias Nyman, Oskar Sandberg, Simon Sandén, and Ronald Österbacka I owe a great deal of appreciation for their welcoming, collaborative approach to research during my three month visit to Åbo Akademi University in the city of Turku, Finland. I left Turku with a great deal of wonderful memories and a fierce interest in materials physics that will always be attributable to my interactions with this amazing cohort.

I gained tremendous insights into an array of experimental techniques during my time at Johns Hopkins University. Dr. Patricia McGuiggan was a fantastic teacher and expert instructor as I learned atomic force microscopy under her tutelage. Prof. Daniel Reich and Dr. Brian Kirby at NIST's Center for Neutron Research were fantastic instructors on the analysis of x-ray and neutron scattering of organic thin films. Huy Vo was an indispensable resource in the Biomedical Engineering Microfabrication Laboratory, and his sound advice saved me much time and spared me significant frustration throughout my time here.

My mother, Molly A. Hardigree, has always been the greatest supporter of my academic pursuits, encouraging my interest in science from a very young age and at every step since kindergarten. Self-anointed as my "#1 cheerleader," her lifelong efforts have in no small part helped me reach this step of my professional career. Likewise, my family members Molly A. Martínez Hardigree, Jorge A. Negron Lugo, and Felipe Martínez Arroyo, are most deserving of acknowledgement for their continued support and love. Outside the laboratory, I am also very

thankful to Dr. Susan Boswell for having been a ready ear when the stresses of the Graduate Representative Organization or of my own experiments ran high.

Daniel Yelin and Angela Feldhaus hold a special place in my heart. They have generously contributed their open minds and comfortable couches; they have endured my longwinded diatribes on the inexhaustible uses for functional organic electronics; and above all they have reminded me when to have fun and relax. I will always be indebted to Angela for having first pushed me to see the world through the lens of physics.

## **Table of Contents**

| Chapter 1 : Introduction to Metal-Insulator-Semiconductor (MIS) Diodes  |                         |

|-------------------------------------------------------------------------|-------------------------|

| Effect Transistors                                                      |                         |

| Organic Field-Effect Transistors                                        | 5                       |

| Transistor Operation                                                    | 9                       |

| Deviations from inorganic theory                                        | 12                      |

| Equilibrium vs. Kinetics in Transistors                                 | 13                      |

| Tuning the Threshold Voltage in Organic Field-Effect Transistors        | 16                      |

| Introduction                                                            | 18                      |

| Triode-corona charging                                                  | 20                      |

| Pre-polarization by Gate stressing                                      | 22                      |

| Floating and Dual Gates                                                 | 23                      |

| Self-assembled monolayers                                               | 24                      |

| Physisorbed layers                                                      | 30                      |

| Challenges Ahead and Outlook                                            | 31                      |

| References                                                              | 32                      |

| Chapter 2 : Reducing Leakage Currents in n-Channel Organic Field-effect |                         |

| Molecular Dipole Monolayers on Nanoscale Oxides                         |                         |

| Introduction                                                            | 37                      |

| Results and Discussion                                                  | 39                      |

| OFET Device Performance                                                 | 39                      |

| Threshold Voltage Shifts                                                | 49                      |

| Switching Behavior                                                      | 50                      |

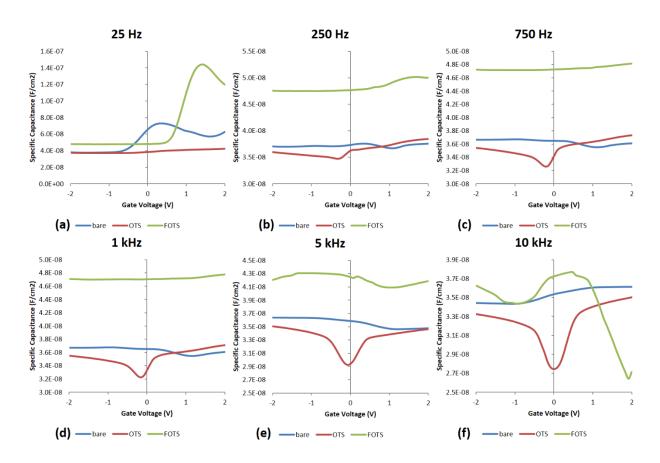

| Capacitance measurements                                                | 53                      |

| Summary and Conclusions.                                                | 54                      |

| Experimental Section                                                    | 55                      |

| Oxides                                                                  | 55                      |

| OFETs                                                                   | 60                      |

| Surface Potentials                                                      | 60                      |

| References                                                              | 61                      |

| Chapter 3: Characterizing Self-Assembled Monolayer-treated oxides with  | thin a Metal-Insulator- |

| Semiconductor Junction                                                  | 63                      |

| Measuring Molecular Dipoles                                                                                         | 63  |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Understanding SAM-induced surface states                                                                            | 67  |

| Oxide + SAM MIS Diodes                                                                                              | 68  |

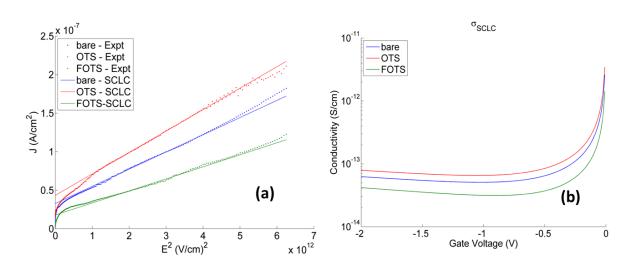

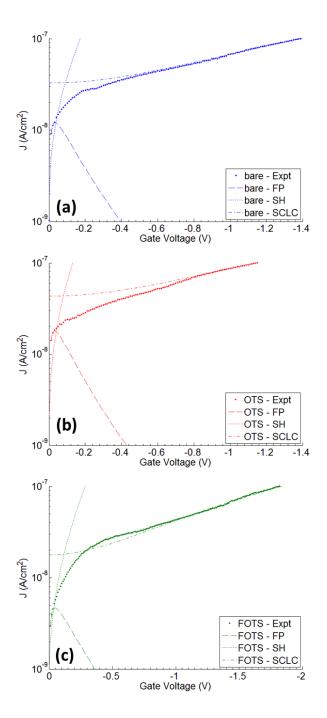

| J-V Characteristics of SAM-treated MIS Diodes                                                                       | 72  |

| Models for MIS Diode Conduction                                                                                     | 73  |

| Space-Charge Limited Conduction (SCLC)                                                                              | 73  |

| Schottky Emission                                                                                                   | 74  |

| Frenkel-Poole                                                                                                       | 75  |

| Diode Analysis                                                                                                      | 76  |

| 8-2-Bn NTCDI OFET Gate Stack                                                                                        | 80  |

| Side note: Morphology vs. Dipoles                                                                                   | 84  |

| Diodes Comparison                                                                                                   | 86  |

| 5FPE NTCDI Gate Stack                                                                                               | 89  |

| Charge Extraction in a Linearly-Increasing Voltage                                                                  | 94  |

| Conclusions and Future Prospects                                                                                    | 100 |

| References                                                                                                          | 101 |

| Chapter 4 : Visualizing and Quantifying Charge Distributions Correlated to Threshold Venezieral Organic Transistors | _   |

| Introduction                                                                                                        | 105 |

| Results and Discussion                                                                                              | 107 |

| Lateral PS OFET measurements                                                                                        | 107 |

| Quantitative relationship between SKPM-derived and V <sub>T</sub> -shift-derived charge densities                   | 112 |

| Comparison to V <sub>t</sub> data                                                                                   | 116 |

| Conclusions                                                                                                         | 123 |

| Methods                                                                                                             | 124 |

| Experimental                                                                                                        | 124 |

| Numerical Estimation of Charge Density                                                                              | 124 |

| References                                                                                                          | 125 |

| Chapter 5 : Conclusions and Future Prospects                                                                        | 128 |

| Self-Assembled Monolayers                                                                                           | 128 |

| Polymer Insulators                                                                                                  | 131 |

| Appendix A: Measuring SAM Dipoles using Charge Extraction                                                           | 133 |

|                                                                                                                     |     |

| Appendix B: Fabrication of Lateral Transistors | Fabrication of Lateral Transistors | . 14 |

|------------------------------------------------|------------------------------------|------|

|------------------------------------------------|------------------------------------|------|

## **Table of Figures**

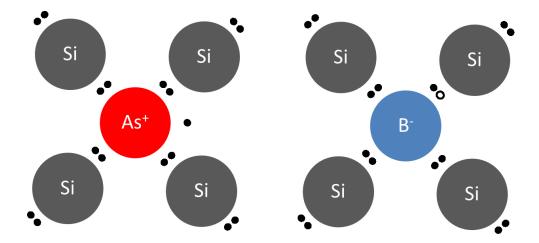

| Figure 1.1 Substitutional doping of silicon with arsenic (boron) to make silicon more n-type (p-type)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

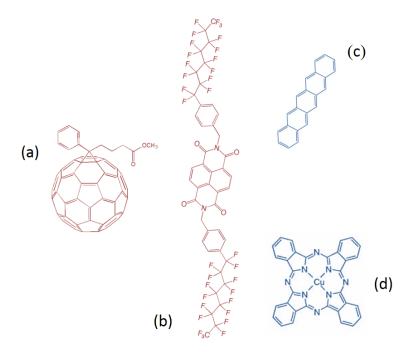

| Figure 1.2 Several electron transporting (red) and hole transporting (blue) small molecules typically employed in OSC thin films. (a) phenyl-C <sub>61</sub> -butyric acid methyl ester (PCBM); (b) 8-0-Bn naphthalene tetracarboxylic diimide (NTCDI); (c) pentacene; (d) copper phthalocyanine (CuPC).                                                                                                                                                                                                                                                                                                                                                                                     |

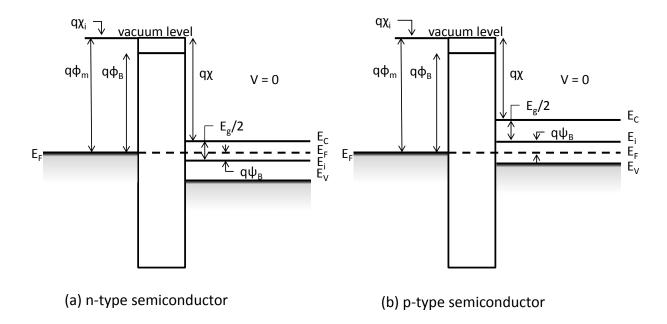

| Figure 1.3 Energy band diagrams of a metal-insulator-semiconductor (MIS) junction at vacuum level for (a) n-type and (b) p-type semiconductors. Energy level for the conduction $(E_C)$ band is determined by the electron affinity $(\chi)$ . Energies corresponding to the semiconductor's Fermi $(E_F)$ , intrinsic $(E_i)$ , and valence $(E_V)$ bands are shown for n-type and p-type semiconductors. Alignment between $E_F$ and the workfunction $(\phi_m)$ are illustrated. Barrier heights between the metal and insulator $(\phi_b)$ and between the Fermi and intrinsic levels $(\psi_B)$ are referenced to the metal work function and semiconductor Fermi levels, respectively. |

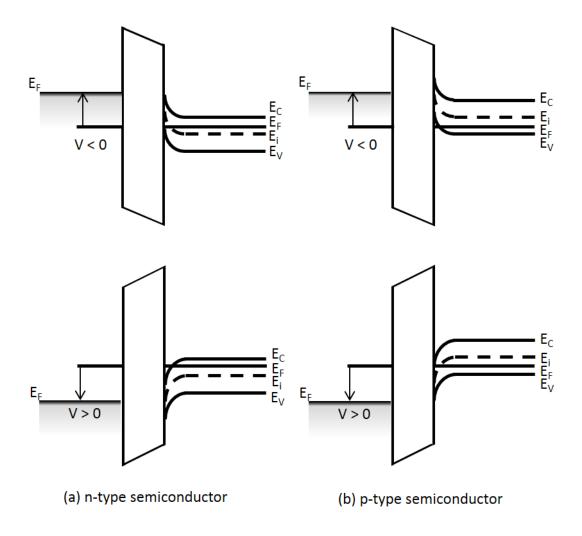

| Figure 1.4 Energy band diagrams of a metal-insulator-semiconductor (MIS) junction for (a) n-type and (b) p-type semiconductors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

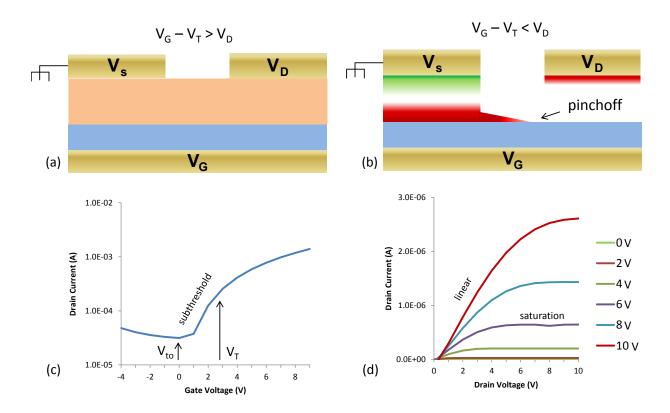

| Figure 1.5 Illustration of a bottom gate/top-contact n-channel accumulation-mode OFET on 100nm SiO2. (a) FET in the linear regime. The gate-drain field (or $V_G - V_D$ ) is smaller than the gate-source field ( $V_G - V_S$ ). The carrier concentration in the transistor channel is mostly uniform throughout when $V_D < V_G - V_T$ , the threshold voltage. (b) Formation of a space-charge region near the drain contact when $V_D = V_G - V_T$ . Saturation occurs when $V_D > V_T$ . (c) Transfer curve for the same device. (d) Output curve for the same n-channel accumulation-mode OFET, with linear and saturation regimes identified.                                         |

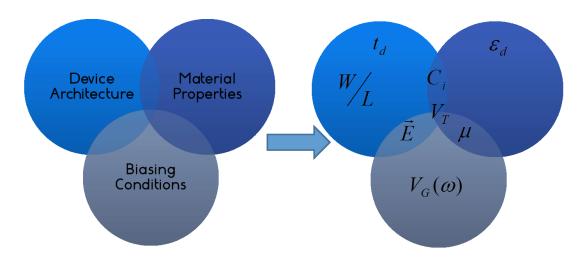

| Figure 1.6 Venn diagram illustrating the relationship between the various parameters that determine the operation of an FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

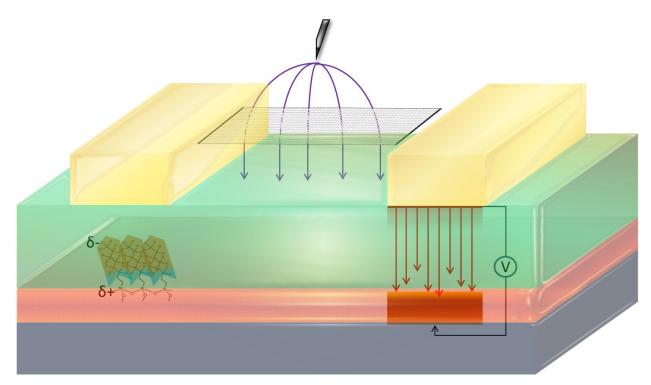

| Figure 1.7 Cross-section of an organic field-effect transistor (OFET) with idealizations of several methods for controlling the threshold voltage. Interfacial molecular dipoles (left), corona/triode charging (center), and gate bias stressing (right).                                                                                                                                                                                                                                                                                                                                                                                                                                   |

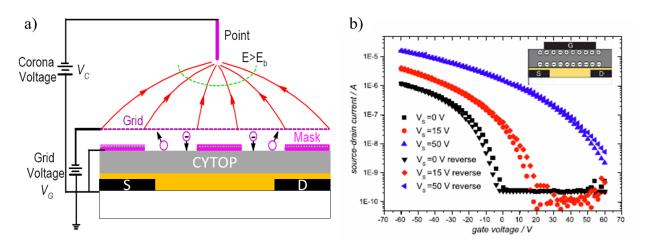

| Figure 1.8 (a) Illustration of triode corona charging of an organic dielectric. The corona voltage $V_C$ between the top and bottom electrodes (as high as -8 kV), and the grid voltage $V_G$ between the grid and bottom electrode (0-60 V), satisfy the relation $V_C >> V_G$ . (b) Output curves for OFETs without corona pre-polarization (hollow squares) and with a dielectric pre-polarized with $V_C = -8$ kV, $V_G = -50$ V, showing much larger $I_D$ under equal biasing conditions. Adapted image from Refs. 34 and 35.                                                                                                                                                          |

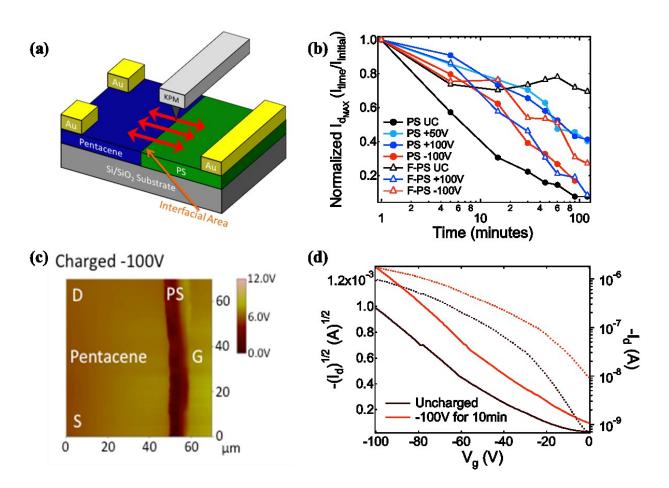

| Figure 1.9 (a) Schematic of a lateral OFET structure in which interfacial potentials can be probed with scanning Kelvin-probe microscopy (SKPM). (b) SKPM surface potential image of lateral OFET, with S, D, and G labeling the Source, Drain, and Gate electrodes, respectively. (c) Decay of the $V_T$ in lateral OFETs with pristine and prepolarized polystyrene (PS) and poly(2-trifluoromethyl styrene) (F-PS) dielectrics. (d) Transfer curves for pristine and pre-polarized OFET with a PS dielectric shown in (b), indicating a decrease in the $ V_T $ towards 0 V. Adapted images from Ref. 23.                                                                                 |

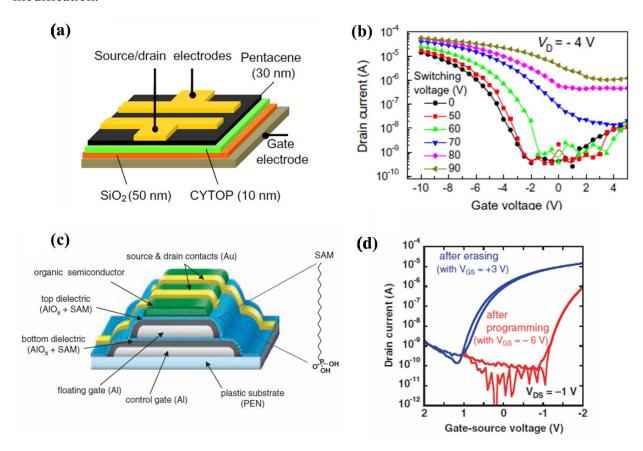

| Figure 1.10 (a) Device diagram of a double-dielectric structure utilizing a CYTOP organic dielectric layer, and (b) transfer characteristics for various writing voltages in a p-channel OFET. Adapted images from Ref. 56. (c) Schematic of a floating gate structure using Al-AlOx for both device and floating gates, and (d) transfer characteristics for a p-channel OFET after programming and erasing steps. Adapted images from Ref. 52                                                                                                                                                                                                                                              |

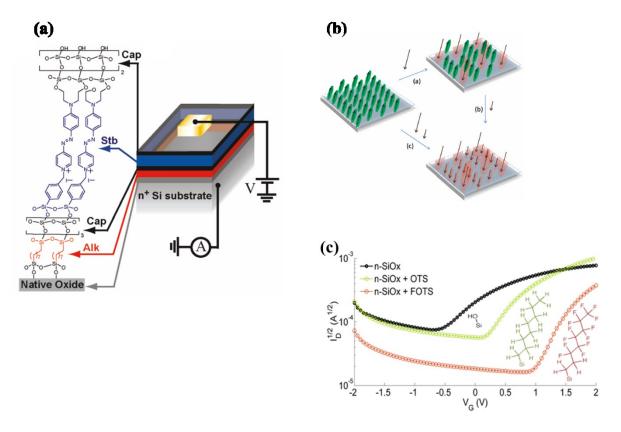

| Figure 1.11 (a) A metal-insulator-semiconductor structure utilizing a self-assembled nanodielectric (SAND) consisting of alkyl and stilbazolium interlayers. Adapted image from Ref. 82. (b) Application of monolayers of OTS and FOTS to a nanoscale silicon oxide shifts V <sub>T</sub> with increasing dipole magnitude, and results in a decrease of the subthreshold leakage for FOTS. Adapted image from Ref. 83. (c) Schematic illustrating the tunability of a substrate surface potential with mixed monolayers of opposite dipoles. Adapted image from Ref. 65.                                                                                                                    |

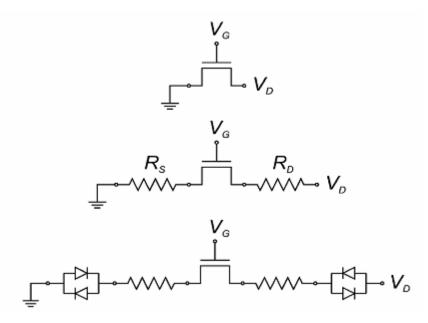

| Figure 1.12 Circuit model incorporating contact resistances at source (RS) and drain (RD) electrodes. Diodes in series with contact resistances account for non-linear injection at the electrode. Image adapted from Ref. 1829                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

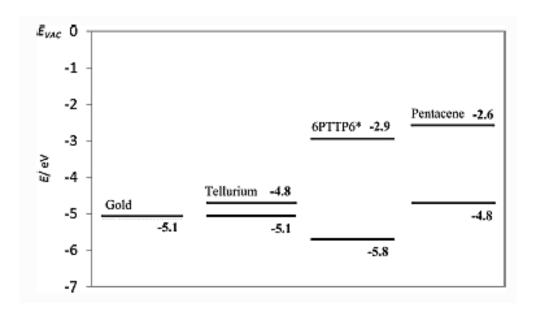

| Figure 1.13 Vacuum-level energy band diagram for hybrid organic/Te OFETs. Image adapted from Ref. 10031                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

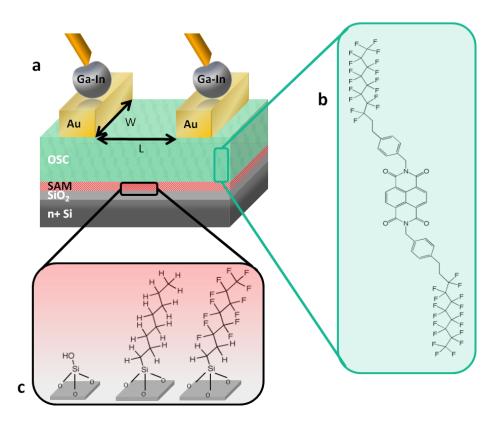

| Figure 2.1 Experimental platform for probing the effect of a molecular dipole. (a) OFET fabricated on a plasmagrown 10 nm minimal oxide with a SAM at the dielectric/OSC interface. (b) Chemical structure of 8-2-Bn NTCDI. (c) Bare oxide and SAM-functionalized oxide with OTS and FOTS.                                                                                                                                                                                                                                                                                                                                               |

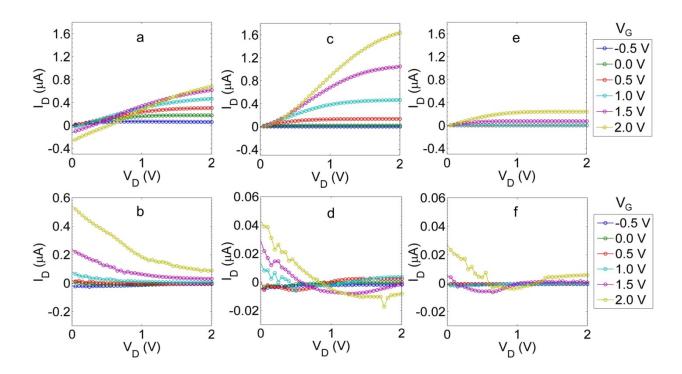

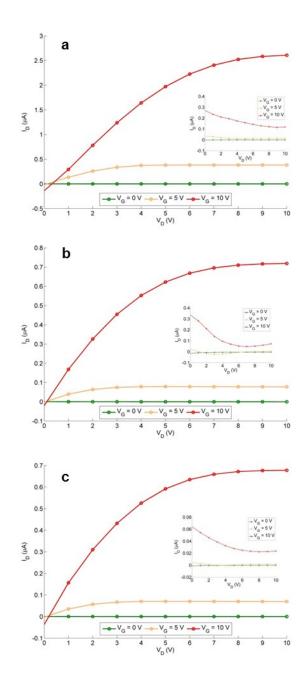

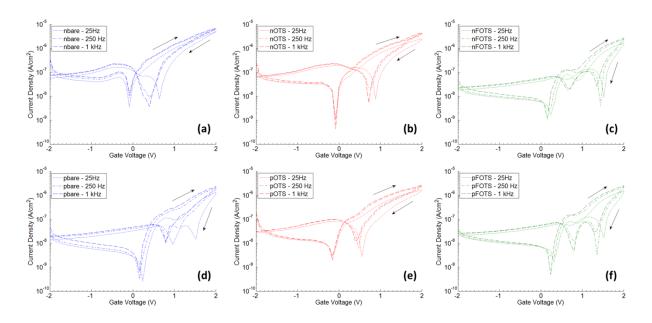

| Figure 2.2 Output (top panels) and leakage (bottom panels) characteristics of 8-2-Bn NTCDI OFETs fabricated on highly-doped n-type silicon with 10 nm plasma-grown oxide. (a-b) Devices on bare oxide. (c,d) Devices on OTS. (e,f) Devices on FOTS; inset shows rescaled output curve. Each curve is of data from averages of three devices on the same substrate for each wafer type. Device W/L ratio is 53.3. Note that the scale for b is 10x the scale for d and f                                                                                                                                                                  |

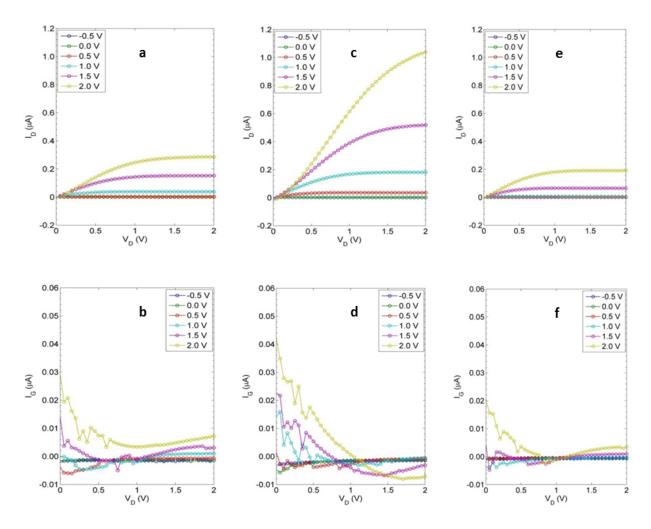

| Figure 2.3 Output (top panels) and leakage (bottom panels) characteristics of 8-2-Bn NTCDI OFETs fabricated on highly-doped p-type silicon with 10 nm plasma-grown oxide. (a-b) Devices on bare oxide. (c,d) Devices on OTS. (e,f) Devices on FOTS; inset shows rescaled output curve. Each curve is of data from averages of three devices on the same substrate for each wafer type. Device W/L ratio is 53.3                                                                                                                                                                                                                          |

| Figure 2.4 OFETs fabricated with 8-2-Bn NTCDI on highly-doped nSi with 100 nm thermally-grown oxide with (a) no treatment and SAM treatments of (b) OTS and (c) FOTS. Insets display leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                     |

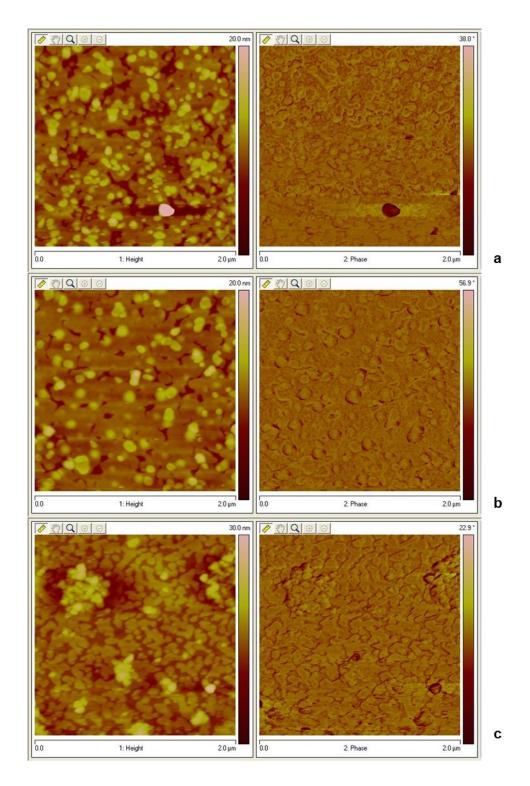

| Figure 2.5 AFM height and phase images of 15 nm of 8-2-Bn NTCDI on n-Si. (a) NTCDI on 10 nm oxide. (b) NTCDI on OTS-treated oxide, displaying a large degree of connectivity between grains. (c) NTCDI on FOTS-treated oxide. NTCDI growth tracks underlying oxide hillocks                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.6 AFM height and amplitude error images of 40 nm of 8-2-Bn NTCDI on n-Si.(a) NTCDI on 10 nm oxide, showing a high degree of polycrystallinity. (b) NTCDI on OTS-treated oxide. (c) NTCDI on FOTS-treated oxide. Amplitude error images of SAM-treated oxides show underlying patches of NTCDI islands                                                                                                                                                                                                                                                                                                                           |

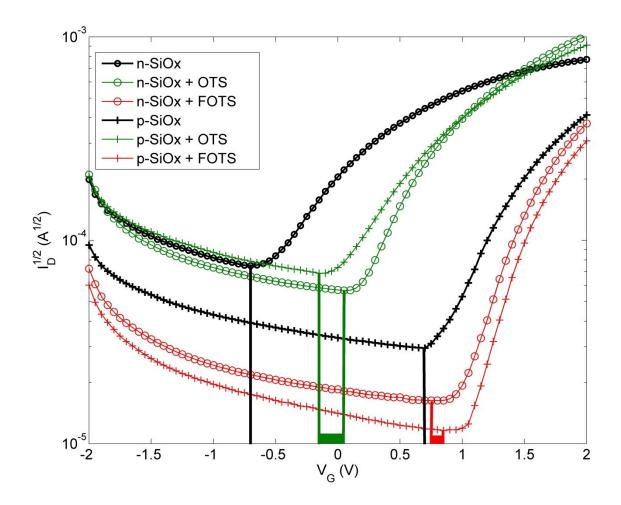

| Figure 2.7 Effect of a molecular dipole on sub-threshold leakage. $I_D^{1/2}$ vs. $V_G$ plot for OFETs with bare oxide, OTS, and FOTS on n-Si and p-Si. Vertical lines for bare oxide (black), OTS- (green), and FOTS- (red) treated OFETs show similar turn-on voltages for SAM-treated OFETs                                                                                                                                                                                                                                                                                                                                           |

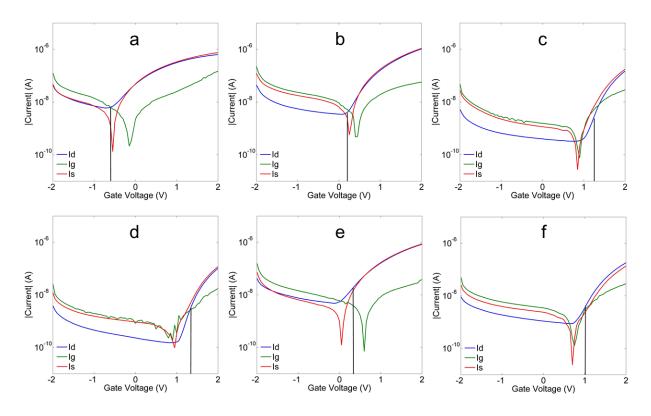

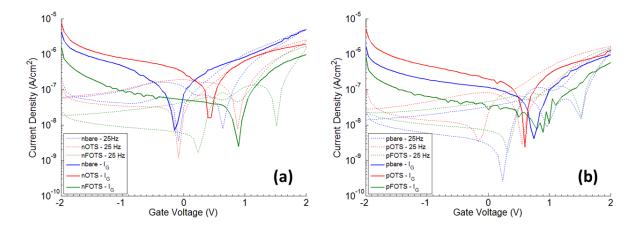

| Figure 2.8 Terminal currents for high-leakage OFETs on n-SiOx (top panels) and p-SiOx (bottom panels). (a-c) Devices on bare, OTS-, and FOTS- treated n-Si oxide, respectively. (d-f) Devices on bare, OTS-, and FOTS-treated p-Si oxide. Vertical lines indicate the $V_T$ as listed in Table 2.2.                                                                                                                                                                                                                                                                                                                                      |

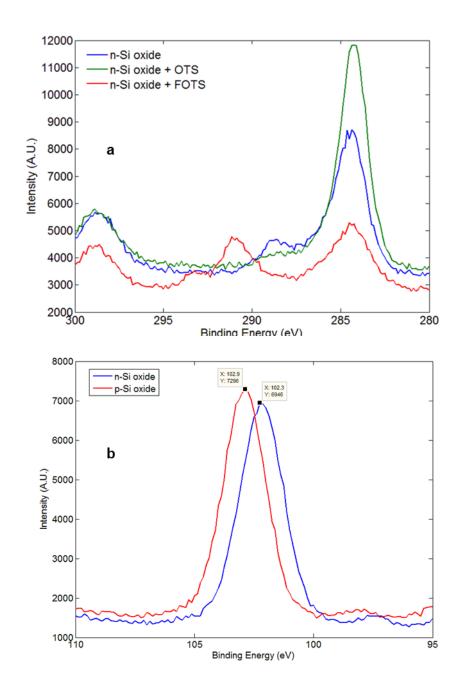

| Figure 2.9 Carbon 1s and Silicon 2p X-ray Photoelectron Spectra of bare and SAM-treated oxides on n-Si. (a) OTS samples show an increase in the peak at 284.5, corresponding to the CH <sub>2</sub> bond. FOTS samples show a distinct double peak at 293 eV and 291 eV, corresponding to the CF <sub>3</sub> and CF <sub>2</sub> bonds. The ratio of the peaks, approximately 5:1, is consistent with the number of CF <sub>2</sub> and CF <sub>3</sub> species on the FOTS molecule. (b) The core Si 2p electrons for p-Si are observed to lie 0.625 eV above those of n-Si. The experimental resolution of the XPS unit is 0.125 eV56 |

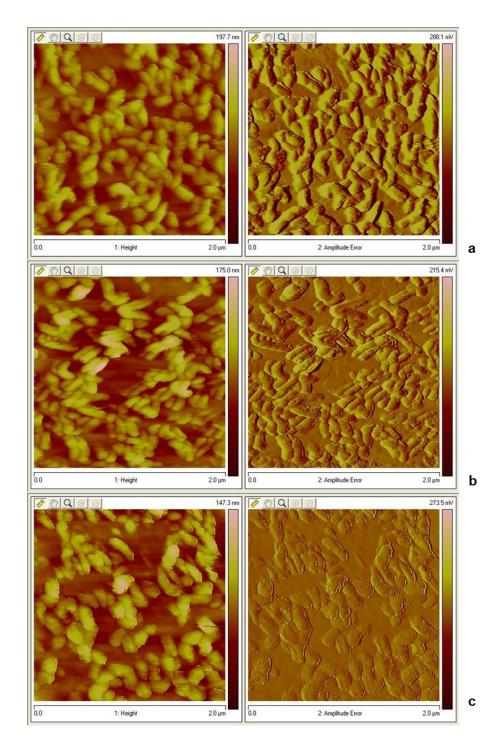

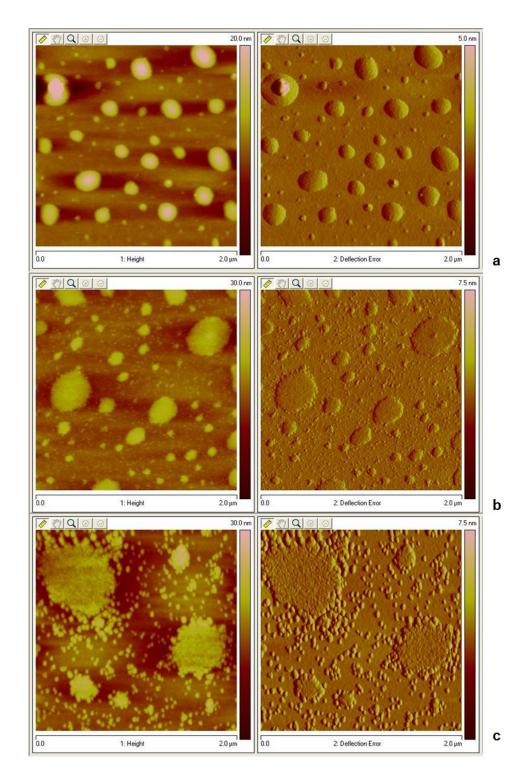

| Figure 2.10 AFM height and deflection error images of rough n-Si oxide surfaces. (a) Rough 10 nm oxide. (b) Rough oxide with OTS treatment. (c) Rough oxide with FOTS treatment, showing SAM domains on oxide hillocks of 2-3 nm height. Larger FOTS-coated oxide hillocks show roughness of $\sim$ 1-2 nm                                                                                                                                                                                                                                                                                                                               |

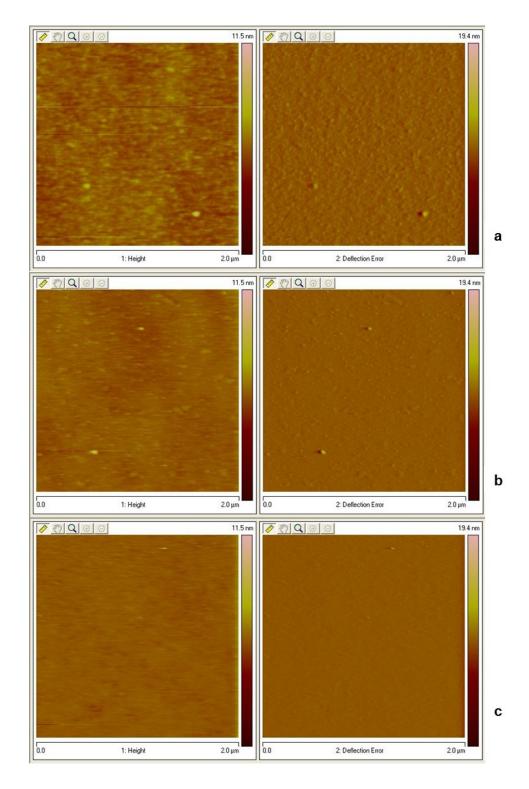

| Figure 2.11 AFM height and deflection error images of smooth n-Si oxide surfaces pre- and post-SAM-treatment. (a) Rough 10 nm oxide. (b) Rough oxide with OTS treatment. (c) Rough oxide with FOTS treatment59                                                                                                                                                                                                                                                                                                                                                                                                                           |

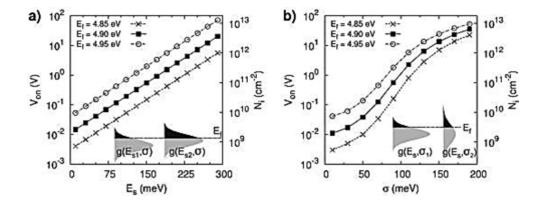

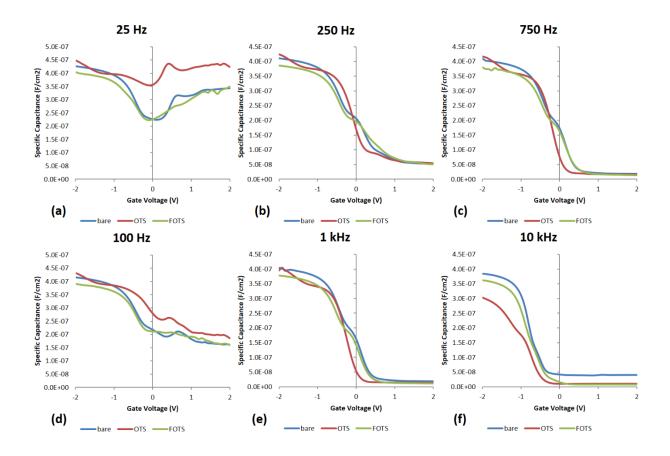

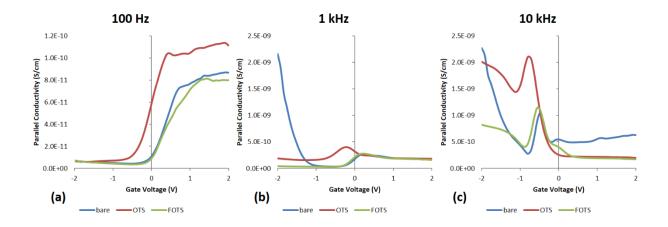

| Figure 3.1 A dipolar SAM layer on an OFET insulator creates energetic disorder at the SAM-OSC interface. Onset voltage $V_{on}$ and equilibrium charge carrier density $N_i$ for OSC with Gaussian DOS where they are have (a) the same energetic disorder $\sigma$ (standard deviation) and different electrostatic interaction $E_s$ ; and where they have (b) identical                                                                                                                                                                                                                                                               |

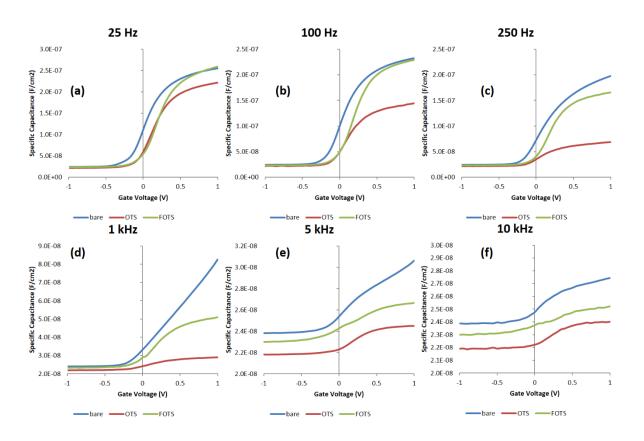

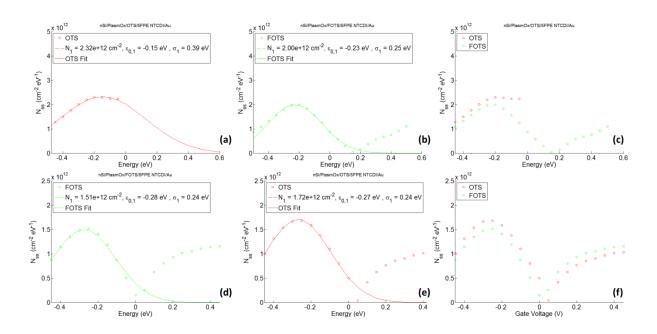

| Figure 3.15 Fits of CV data presented in Fig. 3.13 using Eq. 4.25. (a) OTS, 100 Hz, (b) FOTS, 100 Hz, and (c) comparison of OTS and FOTS, 100 Hz. (d) OTS, 250 Hz, (e) FOTS, 250 Hz, and (f) comparison of OTS and FOTS, 250 Hz. Data corresponds to capacitors using OFET (smaller) electrodes                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

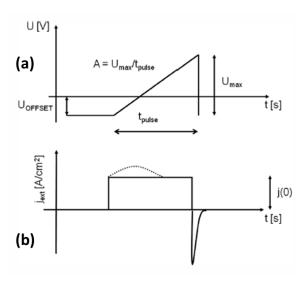

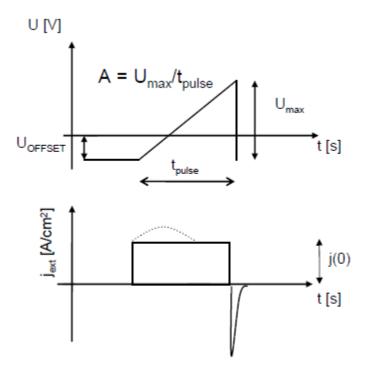

| Figure 3.16 (a) Energy schematic of a CELIV measurement. (b) Current response of the applied voltage ramp <i>A</i> . Image adapted from Ref. 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

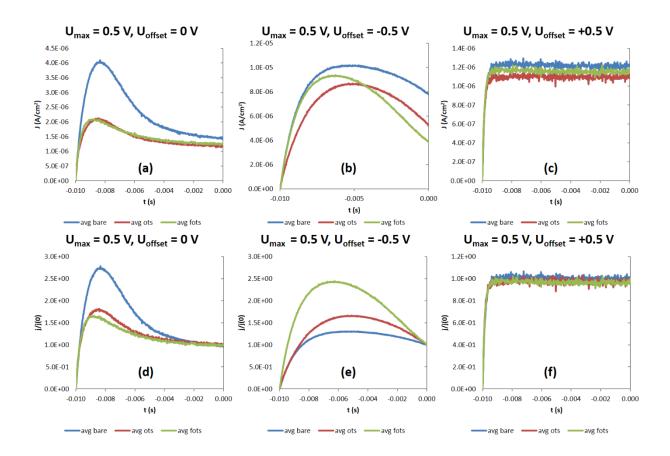

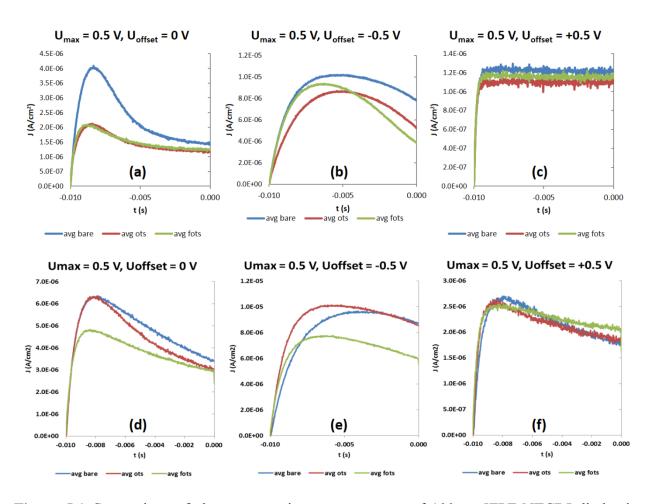

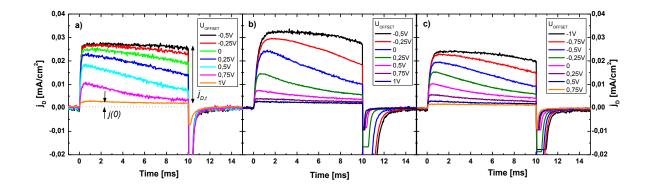

| Figure 3.17 Extracted current transients for nSi/PlasmOx(+SAM)/100 nm 5FPE/Au structures. Voltage ramps of $U_{max} = 0.5 \text{ V}$ for (a) 0V, (b) -0.5 V, and (c) +0.5 V, respectively; and currents are normalized by the current j(0) (d) 0V, (e) -0.5 V, and (f) +0.5 V, respectively. All voltages are relative to the top Au contact                                                                                                                                                                                                                                                                                                                       |

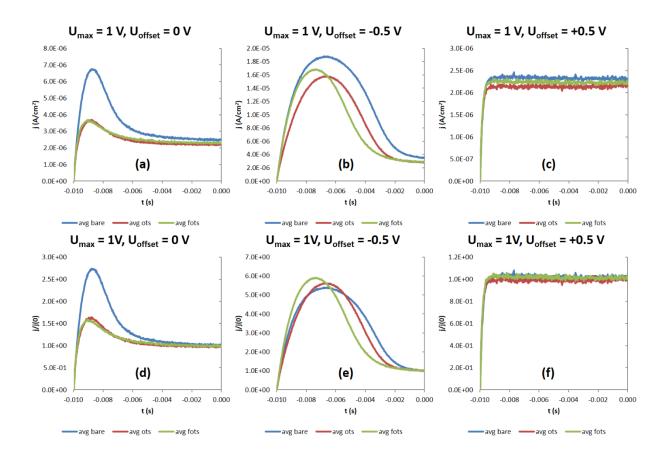

| Figure 3.18 Extracted current transients for nSi/PlasmOx(+SAM)/100 nm 5FPE/Au structures. Voltage ramps of $U_{max} = 1 \text{ V}$ for (a) 0V, (b) -0.5 V, and (c) +0.5 V, respectively; and currents are normalized by the current j(0) (d) 0V, (e) -0.5 V, and (f) +0.5 V, respectively. All voltages are relative to the top Au contact98                                                                                                                                                                                                                                                                                                                       |

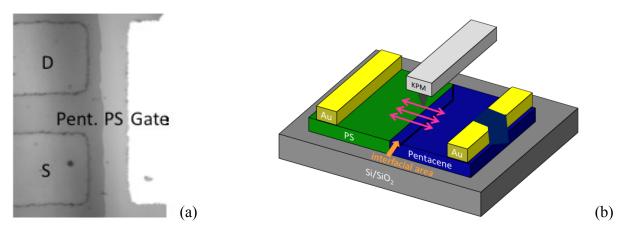

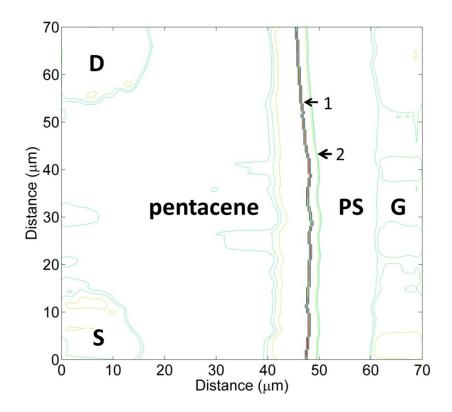

| Figure 4.1 (a) An optical microscope picture of the lateral OFET. Note that the distance between source and drain electrodes is $30 \mu m$ and the distance between the source/drain and gate electrodes is $30 \mu m$ . About half (+/- a quarter) of the source/drain to gate distance is taken by the PS region. (b) Schematic of the SKPM scanning direction "x", parallel to the double arrows.                                                                                                                                                                                                                                                               |

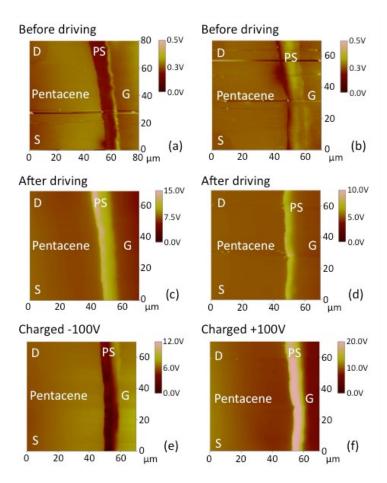

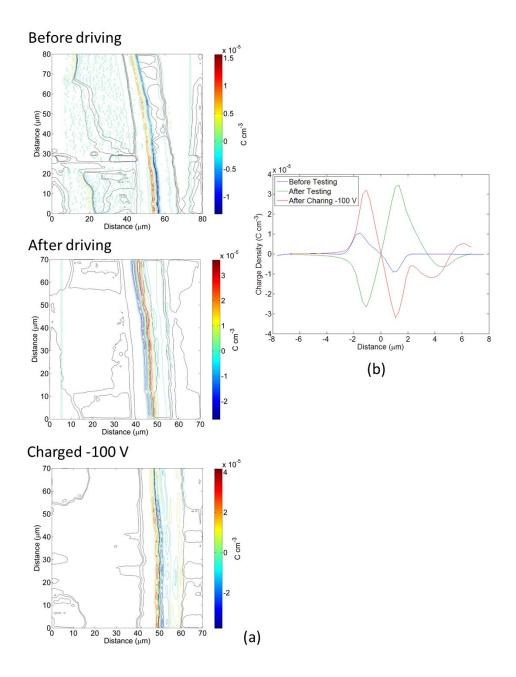

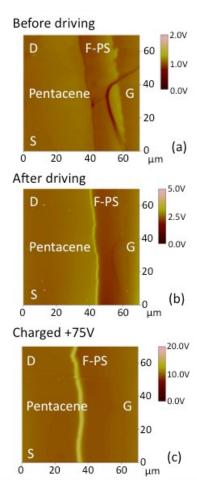

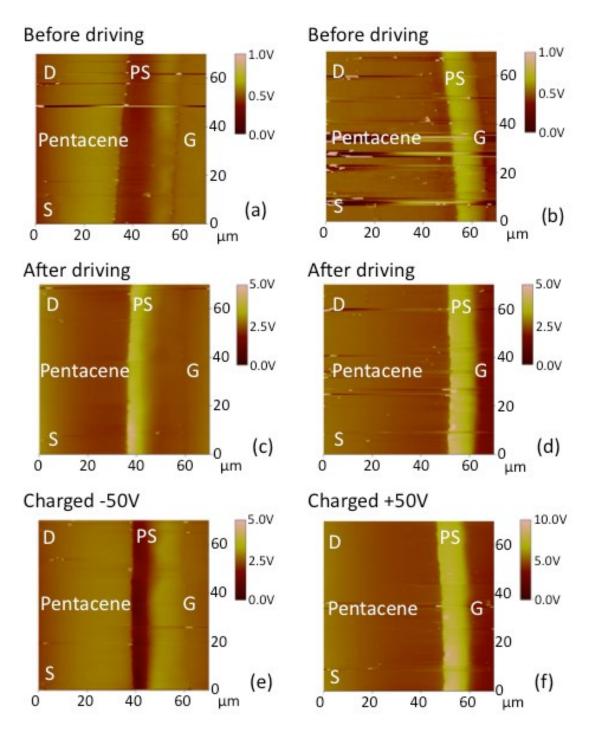

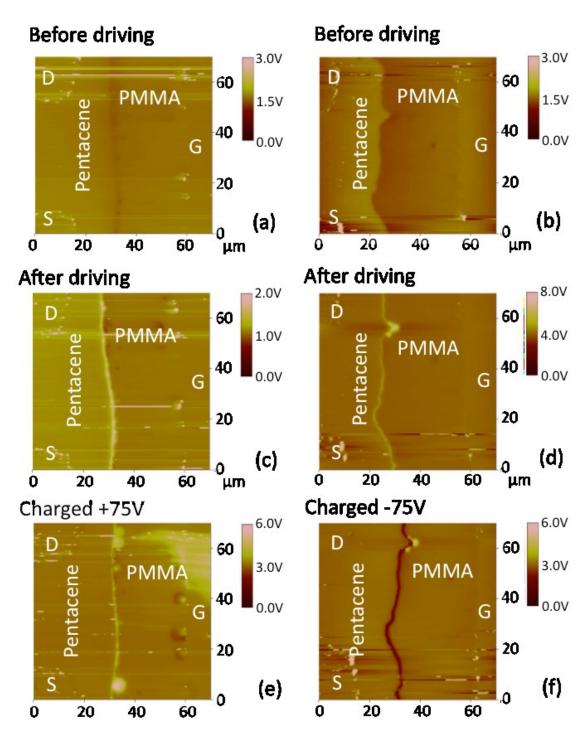

| Figure 4.2 SKPM surface potential scans of lateral PS transistors. The source and drain electrodes, though difficult to see, are always at the left of the image and the gate is at the far right. The pentacene is on the left and the PS on the right of the interface. Images (a,c,e) and (b,d,f) correspond to individual samples. The samples are first imaged before electrical testing (a,b). After the transistor electrical measurements, the samples are scanned (c,d). The samples were then charged to -100 V (e) and +100 V (f) for 10 minutes and rescanned. The correspond height scans can be seen in Appendix B Figure B.2.                       |

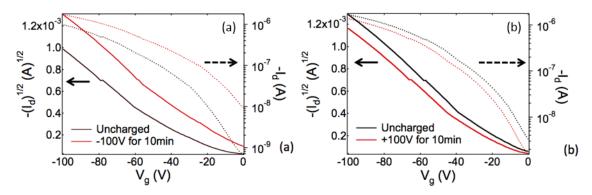

| Figure 4.3 Transfer curves for the samples shown in Fig. 4.2. The black curves were obtained before the samples are charged, while the red curves were from samples after charging. The dashed line corresponds to the log scale while the solid line is the square root of the drain current. The samples were charged to -100 V (a) and +100 V (b)111                                                                                                                                                                                                                                                                                                            |

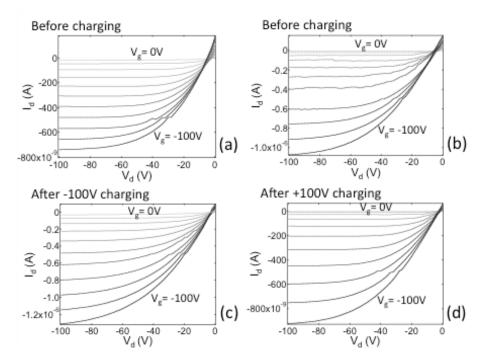

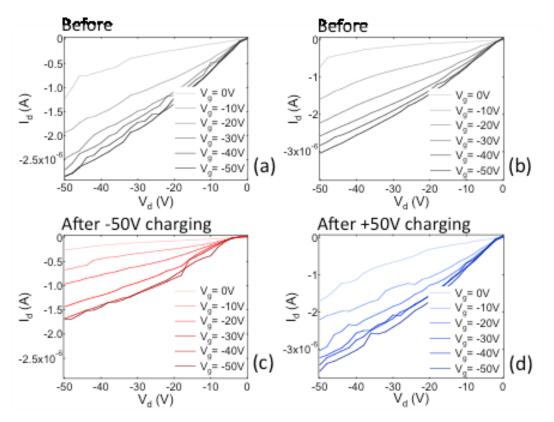

| Figure 4.4 Output curves for the transistors in Fig. 4.2, before (a) and after (c) -100 V charging and before (b) and after (d) +100 V charging. Note the slightly different y-axes. The gate voltage was stepped from 0V to -100V in -10V increments.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.5 Illustration of height profile contour of the OFET illustrated in Fig. 4.2. The line indicated by 1 corresponds to the sharp ridge at the PS-pentacene interface indicated by the height scan. The line indicated by 2 corresponds to the edge of the PS-pentacene interface as approximated by the contouring algorithm                                                                                                                                                                                                                                                                                                                                |

| Figure 4.6 (a) Charge Density Maps of OFET from Fig. 4.2.Before driving, the device shows a small amount of charge at the PS-pentacene interface, consistent with its surface potential plot. Before driving, the PS near the pentacene interface is more negative than the adjacent pentacene layer. After driving, the PS at the interface becomes more positive than the pentacene, the result of driving holes into the PS layer. Upon charging to -100 V for 10 min, the PS layer is more negative than the adjacent pentacene layer, and has significant charge extending into the PS. (b) Corresponding cross-section of charge density illustrated in (a). |

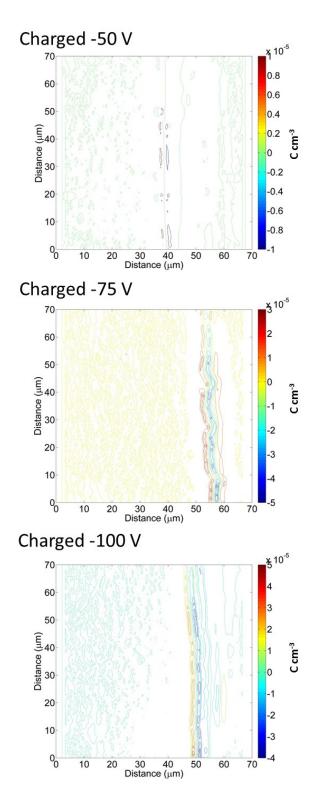

| Figure 4.7 Comparison of charge density distribution for OFETs charged to -50 V, -75 V, and -100 V, respectively. All images have been contoured using 13 levels, spaced in 10 $\mu$ C cm <sup>-3</sup> increments from -60 to 60 $\mu$ C cm <sup>-3</sup> 117                                                                                                                                                                                                                                                                                                                                                                                                     |

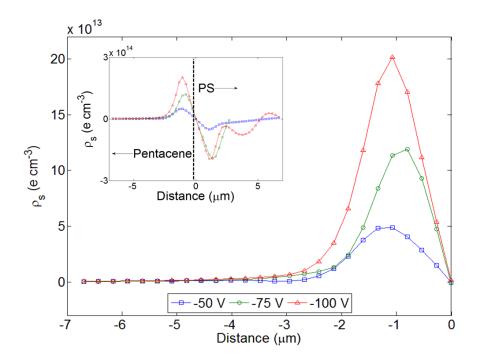

| Figure 4.8 Charge density on the pentacene side, and (inset) across the PS-pentacene interface in each charged OFET (median of 256 linescans per OFET). The increase in accumulated positive charge density in the pentacene layer with increasing charging voltage is consistent with the observed $V_t$ shift for these OFETs                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.9 SKPM surface potential scans of the F-PS lateral transistors. The interface has the pentacene on the left and the F-PS on the right. The electrodes are oriented in the same manner as Fig. 4.2. (a) The samples are first                                                                                                                                                                                                                                                                                                                                                                                                                              |

| imaged before electrical testing. (b) After the transistor electrical measurements the samples are scanned. (c) The sample was then charged to a value of +75V for 10 minutes and rescanned. The corresponding height scan can be seen in the Appendix B, Fig. B.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

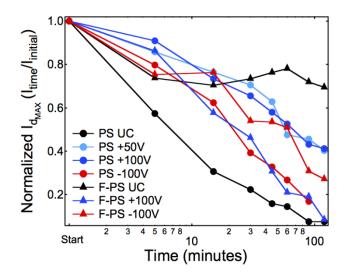

| Figure 4.10 Bias stress behavior of PS (circles) and F-PS (triangles) OFETs. The level of positive charge in the PS samples did not seem to change the gate bias behavior of the OFETs. Positive charging helped the PS sample more than the F-PS. The F-PS performed best with no charging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4.11 Output curves for lateral OFETs without a polymer gate material layer. A sample was tested before (a) and after (c) charging at -50V for 10 minutes, and before (b) and after (d) charging at +50V for 10 minutes. Now that the lateral OFETs have no gate material layer the charging voltage reverses the change in output current, with the negative charging giving lower current and the positive charging giving higher current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 5.1 Comparison of charge extraction measurements of 100nm 5FPE-NTCDI diodes in which the 5FPE was deposited at 0.2 Å/s (a-c) and at 1 Å/s (d-f)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure A.1 Schematic view of the CELIV method.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

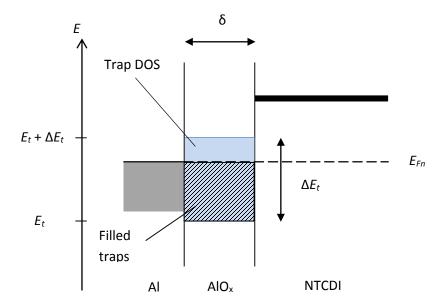

| Figure A.2 Schematic of the trap DOS in AlOx under flatband conditions. $E_{Fn}$ is the quasi Fermi level, $E_t$ is the lowest lying trap level, $\Delta E_t$ is the width of the trap distribution and $\delta$ is the thickness of the oxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure A.3 CELIV current transients at different offset voltages for (a) an Al/AlO $_x$ /NTCDI/Au device (b) an Al/OTS/AlO $_x$ /NTCDI/Au device and (c) an Al/FOTS/AlO $_x$ /NTCDI/Au device. The voltages are applied to the Au contact and $A = +0.5$ V/10ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

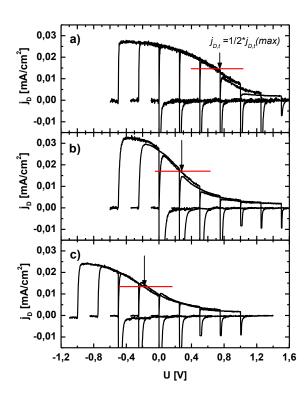

| Figure A.4 The displacement current as a function of voltage for (a) an Al/AlO <sub>x</sub> /NTCDI/Au device (b) an Al/OTS/AlO <sub>x</sub> /NTCDI/Au device and (c) an Al/FOTS/AlO <sub>x</sub> /NTCDI/Au device. The voltages are applied to the Au contact and $A = +0.5$ V/10ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

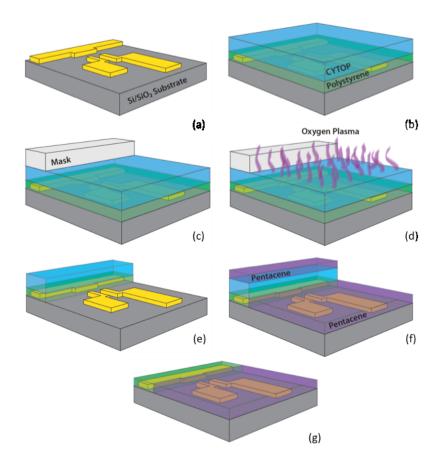

| Figure B.1 Schematic of the fabrication process for the lateral OFETs. (a) 50 nm gold electrodes with a 5 nm Cr adhesion layer are deposited on the Si/300 nm SiO <sub>2</sub> substrate via photolithography. (b) Atactic polystyrene (MW 50,000g/mol) (20 mg/mL in toluene) or poly (3-trifluoromethyl)styrene, (F-PS, 10 mg/mL in tetrahydrofuran) or poly(methyl methacrylate) (PMMA, 20 mg/mL in chlorobenzene, heated at 80 °C to dissolve) is then deposited via spin coating at 2000 RPM for PS and PMMA, and 1000 RPM for F-PS. The sample is annealed at 95°C for 10 minutes and allowed to cool to room temperature. Cytop is deposited via spin coating at 2000 RPM and annealed at 95°C for 10 minutes. (c) A physical mask is placed on the substrate so that the edge of the mask is in the gap between the source/drain electrodes and the gate electrode. (d) Oxygen plasma at medium power is used to remove the unmasked polymer layers. (e) Once the organic layer has been removed from above the source/drain electrodes the OSC can be deposited. (f) 50 nm of pentacene is thermally evaporated at 0.3 Å/s. (g) The Cytop layer is then removed with perfluorodecalin, exposing the interface between the polymer and pentacene |

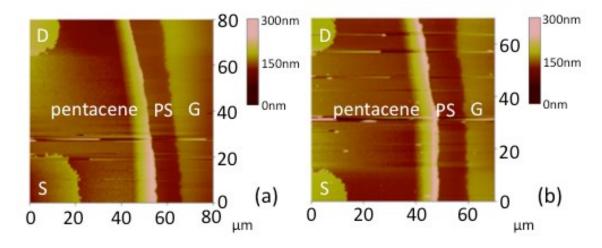

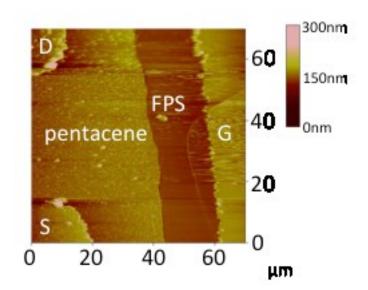

| Figure B.2 Height scans of the two samples from Figure 2 in the main text. The source (S), drain (D) and gate (G) are indicated in addition to pentacene and PS. Note that the edge of the pentacene closest to the PS has a slight height increase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure B.3 KPM scans of two separate samples (a,c,e) (b,d,f). In all images the source and drain electrodes are on the top and bottom of the left side while the gate electrode is on the right side. The samples are first imaged before electrical testing (a,b). After the transistor electrical measurements the samples are scanned (c,d). The samples were then charged to -50 V (e) and +50 V (f) for 10 minutes and rescanned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

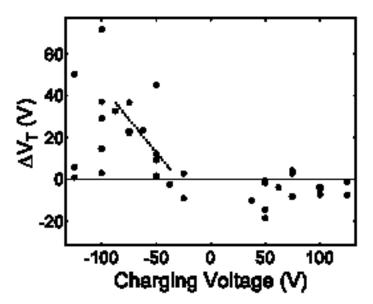

| Figure B.4 Dependence of VT shift on charging voltage. The dotted line indicates the region where the correlation is strong. Above 100 V, the devices break down. At positive charging voltages, the correlation is poorer than for negative charging voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure B.5 KPM height scan from the F-PS sample (Figure 9 main text) with all the features labeled147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure B.6 KPM scans of two separate PMMA samples (a,c,e) (b,d,f). In all images the source and drain electrod                                                                                                                        | des |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| are on the top and bottom of the left side while the gate electrode is on the right side. The samples are first imag before electrical testing (a,b). After the transistor electrical measurements the samples are scanned (c,d). The | ;ed |

| samples were then charged to +75 V (e) and -75 V (f) for 10 minutes and rescanned.                                                                                                                                                    | 148 |

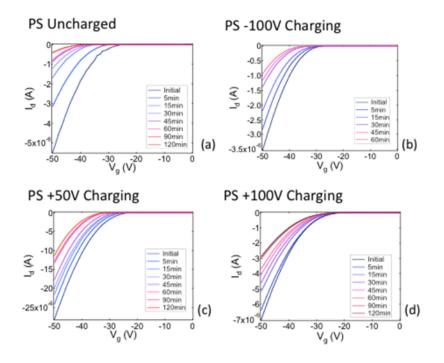

| Figure B.7 Bias stress behavior of PS dielectrics at various charging levels: uncharged (a), -100 V (b), +50 V (c) and +100 V (d). Note the difference in scales.                                                                     | , , |

| (.).                                                                                                                                                                                                                                  |     |

### **List of Tables**

| Table 1.1 Some of the most commonly used oxide dielectrics and compatible SAM anchor groups. For an illustration of SAND layers see Fig. 1.11                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 Leakage currents in n-channel NTCDI OFETs on bare and SAM-treated n-Si and p-Si oxides. $I_G$ currents are gate leakage under several biasing conditions. $^1$ OFF drain current measured from $I_D$ - $V_D$ curves. $^2$ OFF drain current measured from $I_D$ - $V_G$ curves                                                                                                                                                                                                                                                                                |

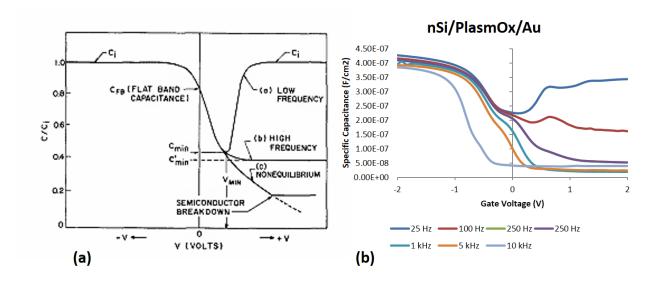

| Table 2.2 Comparison of OFET device parameters for bare and SAM-treated oxides. Threshold voltages, mobility $\mu_{meas}$ , and sheet transconductance values were extrapolated from $I_D^{1/2}$ vs. $V_G$ plots. Specific capacitance was measured at 100 Hz, using an electrode area of $3.03 \times 10^{-2}$ cm <sup>2</sup> . ON/OFF ratios were measured from $V_{to}$ to 2 V. Device W/L ratio is 53.3.                                                                                                                                                           |

| Table 3.1 Comparison of extracted parameters for bare, OTS-, and FOTS-treated oxide MIS structures.  Abbreviations <i>FP</i> – Frenkel-Poole; <i>SH</i> – Schottky; <i>SCLC</i> – Space charge-limited current                                                                                                                                                                                                                                                                                                                                                          |

| Table 3.2 Device and material parameters for MIS structures investigated. $d$ is the layer thickness, $\mu_{\text{FET}}$ is the field-effect mobility, $\mu_{\text{i}}$ is the intrinsic mobility, and $\varepsilon$ is the dielectric constant of the film                                                                                                                                                                                                                                                                                                             |

| Table 3.3 Extracted vertical drift mobility for gate stack structures with 100 nm 5FPE NTCDI. Note: $A = U_{max}/t_{pulse} = (1 \text{ V}/10 \text{ ms})$ and (0.5 V/10 ms). $\mu_{FET}$ is extracted from OFET measurements on similar gate stacks                                                                                                                                                                                                                                                                                                                     |

| Table 4.1 Geometric and electrostatic parameters for charged OFETs. $t_i$ is the material thickness, $C_i$ is the material specific capacitance, $\Delta V_t$ is the threshold voltage shift, $\sigma_{SKPM}$ is the charge density estimated from the Poisson analysis of the pentacene-side charging and $\sigma_{cap}$ is the charge density estimated from the capacitor approximation. The charge density derived from SKPM data is the charge density integrated on the pentacene side within 2.73 $\mu$ m from the PS-pentacene interface, as shown in Fig. 4.8. |

## Chapter 1 : Introduction to Metal-Insulator-Semiconductor (MIS) Diodes and Organic Field-Effect Transistors

Semiconductors are a class of materials whose electrical conductivity can be modified across a wide range, from that of an insulator to that of a metal. A broad spectrum of electronic devices harness these changes in a semiconductor's conductivity through illumination (solar cells), heating and cooling (thermoelectric generators), the adsorption of chemical species (gas sensors), and the application of an electric field (diodes, transistors, light-emitting diodes). In each device, the material is designed to achieve the greatest change in conductivity for the given external input. Understanding the structure of a semiconductor is critical if control is to be exercised over its electronic properties.

An inorganic semiconductor consists of atoms arranged in a periodic 3-dimensional lattice. The periodicity of the crystal results in an overlap of the electron orbitals of each individual atom, which collectively create bands of allowed energy ranges, separated by regions of forbidden energy ranges. This forbidden energy range is termed the *bandgap*. In an intrinsic semiconductor at a temperature of 0 K, all of the electrons in the semiconductor reside in the lowest energy band, called the valence band. The next available allowed energy band, called the conduction band, is completely empty at 0 K. As the temperature increases, electrons in the valence band will acquire thermal energy, which at room temperature is equivalent to 26 meV.

For many inorganic semiconductors, whose bandgaps can range from ~0.6 - 1.5 eV, it would be impossible for an electron to be thermally excited across the bandgap. However, impurities in the material can create localized states with energies that fall within this bandgap. If the energy of this impurity state is located sufficiently close to the valence band, an electron within the valence band may acquire enough energy to occupy that state, leaving behind an empty state in the valence band below. This absence of an electron in the valence band is called a hole, and the impurity that traps the electron is called an acceptor. Similarly, if an impurity state in the bandgap is located sufficiently close to the conduction band, an electron from the impurity may acquire enough energy to populate a state in the conduction band; these impurities are called

donors. Precise control over the type and density of these impurities is known as doping, an illustration of which is shown in Fig. 1.1.

**Figure 1.1** Substitutional doping of silicon with arsenic (**boron**) to make silicon more n-type (**p-type**).

As a consequence of doping, not only is the quantity of free carriers changed, but also the *type* of carrier, as an increase in impurities just above the valence band will yield an excess of (+) holes, and an increase in impurities just below the conduction band will yield an excess of (-) electrons, relative to the intrinsic semiconductor. These two types of doping yield films that are referred to as p-type and n-type, so called for the abbreviation of the sign (positive/negative) of mobile charge carrier whose concentration they increase.

**Figure 1.2** Several electron transporting (red) and hole transporting (blue) small molecules typically employed in OSC thin films. (a) phenyl- $C_{61}$ -butyric acid methyl ester (PCBM); (b) 8-0-Bn naphthalene tetracarboxylic diimide (NTCDI); (c) pentacene; (d) copper phthalocyanine (CuPC).

By contrast with inorganics, organic semiconductors (OSCs, Fig. 1.2)—thin films of conjugated organic molecules—do not have a large number of intrinsic free carriers. Because of their much larger bandgaps (typically 2-3 eV), electrons cannot be easily thermalized from the highest occupied molecular orbitals (HOMO) to the lowest occupied molecular orbitals (LUMO). Whereas a thin film of intrinsic Si might contain carriers at a concentration of ~10<sup>10</sup> cm<sup>-3</sup>, and a Si film found in an operational electronic device might contain carrier concentrations of 10<sup>18</sup> cm<sup>-3</sup> or greater, typical intrinsic carrier levels in OSCs might be as low as 10<sup>1</sup>-10<sup>5</sup> cm<sup>-3</sup>, and unintentional doping due to impurities<sup>1</sup> might increase this density to 10<sup>14</sup> cm<sup>-3</sup>.

The first organic materials to show promising charge transport were polymers such as polyacetylene, for which Alan Heeger, Alan MacDiarmid, and Hideki Shirakawa were awarded the Nobel Prize in Chemistry in 2000. Charge transport in these polymers was achieved by chemically doping the films with compounds that chemically reduced the conjugated chains. Heeger and co-workers used the vapors of binary halides such as Br<sub>2</sub> and I<sub>2</sub> to dope films of polyacetylene<sup>2</sup>. By introducing these electron-accepting dopants and making available sites with electronic resonance along the chains, carrier mobility was increased from negligibly low (10<sup>-4</sup>).

S/cm) to industrially relevant ( $\sim$ 1 S/cm). This approach has been employed in the fabrication of the now ubiquitous conductive inks poly(3,4-ethylenedioxythiophene):polystyrene sulfonate (PEDOT:PSS)<sup>3</sup>. Although still below the mobility of doped Si ( $10^2$  -  $10^3$  S/cm), the ability to control the conductivity of thin films of conjugated organic compounds has fueled the study and design of thin films and materials for OSCs.

Coupled with low intrinsic carrier densities in pristine OSCs is the low degree of carrier delocalization within these films, which can range from just a few conjugated cores to several nm within the OSC<sup>4</sup>. Films made of highly-ordered semicrystalline polymers such as P3HT and recently PBTTT, as well as prototypical acenes like pentacene and di-imides like NTCDI, have been well modeled with traditional concepts from the inorganic lexicon. However, investigations of carrier transport in many of these polymers and other disordered organic materials has been demonstrated to not follow band-like behavior with few exceptions<sup>5</sup> substantially below room temperature.

Instead, transport is more accurately described by a hopping mechanism<sup>6-8</sup>, which defines carriers as existing in a 3-dimensional Gaussian density-of-states (DOS) through which they sample the space under the influence of an electric field. The presence of grain boundaries as well as chemical impurities all act to change the landscape through which carriers hop. Polymorphs (in the case of evaporated semicrystalline small molecules) can also affect intermolecular distances between conjugated cores<sup>9</sup>, with greater core-to-core distances reducing the probability of a hop. In a recent report, it has been shown that the thermal motion between two neighboring pentacene molecules in a crystal reduces the hopping probability between neighboring molecules<sup>10</sup>, negatively impacting the carrier mobility of the film. Such behavior may appear contrary to inorganics, where thermal excitation of the lattice at room temperature promotes carriers from dopant atoms to their target bands, increasing the conductivity of the semiconductor. Through advances in understanding unconventional, disordered semiconductors such as amorphous silicon<sup>11</sup>, quantities including the mobility<sup>7</sup> and carrier diffusivity<sup>12-14</sup> have been modeled within this framework with satisfactory results.

Despite the differences between charge transport mechanisms within inorganic and organic semiconductors, the design and synthesis of OSCs that preferentially transport holes or electrons has enabled the fabrication of electronic devices with properties analogous to those of inorganic

materials. As a result, the characterization tools used to evaluate inorganic devices have been heavily borrowed, occasionally indiscriminately, to the characterization of those based on OSCs. In the following section, the basic operation of a field-effect transistor is discussed, starting with fundamental operating principles derived for inorganic materials. Where appropriate, differences in operation between organic and inorganic field-effect transistors is discussed.

#### **Organic Field-Effect Transistors**

One of the main considerations for OSCs is their use in digital logic, the main component of which is the transistor. The main transistor architecture investigated in the context of OSCs—and a main subject of this dissertation—is the field-effect transistor (FET). A conventional [inorganic semiconductor] FET derives its name from the concept of a "transfer resistor," and builds on the concept of a metal-insulator-semiconductor (MIS) junction.

**Figure 1.3** Energy band diagrams of a metal-insulator-semiconductor (MIS) junction at vacuum level for (a) n-type and (b) p-type semiconductors. Energy level for the conduction ( $E_C$ ) band is determined by the electron affinity ( $\chi$ ). Energies corresponding to the semiconductor's Fermi ( $E_F$ ), intrinsic ( $E_i$ ), and valence ( $E_V$ ) bands are shown for n-type and p-type semiconductors. Alignment between  $E_F$  and the workfunction ( $\varphi_m$ ) are illustrated. Barrier heights between the metal and insulator ( $\varphi_b$ ) and between the Fermi and intrinsic levels ( $\psi_B$ ) are referenced to the metal work function and semiconductor Fermi levels, respectively.

In an MIS junction (Fig. 1.3), a wide band-gap insulator separates a conductive metal contact from a semiconductor thin film. The metal is defined by its work function  $\phi_m$ , which is the energy required to remove an electron from the surface of the metal. This value is assumed to be a material constant, but can vary by several tenths of an eV depending on the crystallographic facet facing the surface, as well as any impurities at the surface<sup>15</sup>. The semiconductor is defined by its valence and conduction bands. These bands arise from the delocalization of electrons within the semiconductor crystal lattice, and represent the energy levels which charge carriers may occupy within the material.

The gap between the valence ( $E_V$ ) and conduction band ( $E_C$ ) energies is termed the bandgap ( $E_g$ ), and represents energies which carriers are forbidden to occupy (in the absence of doping). The intrinsic energy  $E_i$  is the average energy of an electron in an intrinsic semiconductor, and is roughly halfway in the bandgap. As suggested in the previous section, doping introduces atoms of a greater or lower valence than the host semiconductor atoms, at energy levels within the bandgap. This additional population of states changes the electrochemical potential of electrons in the semiconductor—that is, the Fermi energy  $E_F$ . Since these gap levels can be populated thermally, they can be modeled using Maxwell-Boltzmann statistics. Assuming non-degenerate doping levels, the Fermi level is approximated by the relation

$$E_F - E_C = kT ln \frac{N_C}{N_D}, \text{ (n-type)}$$

[1.1]

$$E_F - E_V = kT ln \frac{N_V}{N_A}, \text{ (p-type)}$$

[1.2]

where  $N_C$  and  $N_V$  are the density of states for the conduction and valence bands, respectively, and  $N_D$  and  $N_A$  are the densities of dopant donor and acceptor atoms, respectively. As the physics of doping falls outside the scope of this thesis, the reader is referred to Ref. <sup>16</sup>.

In an ideal MIS structure, the very low density of conducting states in the insulator makes it impossible for carriers in the semiconductor and metal directly in contact on either side to transit the insulator to reach equilibrium. This lack of available states in the insulator results in a pinning of the vacuum-level ionization and electron affinity energies at the insulator/semiconductor interface. As illustrated in Fig. 1.3, the energy difference between the metal and semiconductor at vacuum level is given as

$$\varphi_{ms,N} = \varphi_m - \left(\chi + \frac{E_C - E_V}{2q} - \psi_B\right)$$

[1.3]

$$\varphi_{ms,P} = \varphi_m - \left(\chi + \frac{E_C - E_V}{2q} + \psi_B\right)$$

[1.4]

where the sign difference of the semiconductor barrier  $\psi_B$  between Eqs. 1.3 and 1.4 reflects the relative potential difference from the intrinsic level  $E_i$  for n-type and p-type semiconductors.

When the materials are connected electrically in a circuit and allowed to reach electrochemical equilibrium (both sides are grounded), the mobile carriers in the semiconductor re-distribute themselves to offset the built-in potential fixed by the difference between the metal work function and the Fermi energy in the semiconductor, as illustrated in Fig. 1.4. Because the electron affinity and ionization potentials are a fixed material property<sup>16</sup>, the difference between the valence and conduction band energies  $E_C$  and  $E_V$ , also remains constant. The difference between  $E_C$  and  $E_V$  relative to  $E_F$  within the proximity of the interface reflects the carrier rearrangement due to the built-in potential and any interfacial dipoles<sup>15</sup>. This re-arrangement is known as band-bending, and is illustrated by the curves adjacent to the insulator. The insulator itself, having no mobile charge carriers, behaves like a resistor. As a result, the electric field across it is distributed linearly between its two surfaces.